牛利民

摘要:本文提出了基于P2020的嵌入式主控单元的硬件设计方案,对主控单元的工作原理进行了说明并对主要模块进行了介绍。该模块已经在实际项目中应用,结果表明该板卡能力突出,工作稳定。

关键词 主控单元 P2020 启动配置

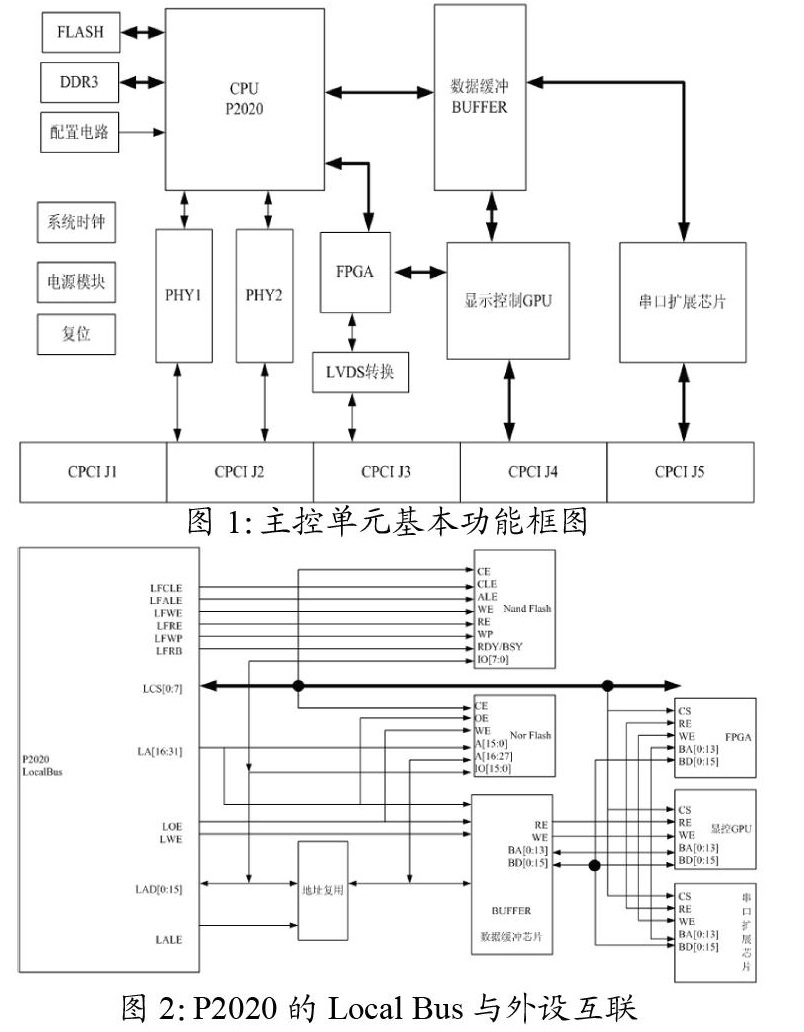

嵌入式主控单元主要功能是承载Vxworks操作系统,主控软件,并负责对业务板卡、信道板卡、交换板卡等其他板卡进行配置、数据交换,以及人机接口,外部接口进行交互功能等。该主控单元具有集成度高、处理能力强、功耗低、扩展性好、环境适应性强等优点,基本功能框图见图1,其中CPU以飞思卡尔的P2020NXE2KFC为核心处理器;内存选用4片256MB /片DDR3 SDRAM;Flash选用64MB Nor FLASH(存放boot程序、操作系统)和16GB Nand FLASH(存放应用程序);千兆以太网物理层控制芯选用两片88E1111,其中一路作为调试网口,一路经母板接交换板;显示控制部分由Xilinx Spartan6 FPGA 、显示控制芯片GPU S1D13513构成;外围接口部分包括串口扩展芯片、两路千兆以太网通过CPCI高速接插件经母板接其他板卡。

1 P2020简介

P2020采用45nm工艺,适用于联网、电信、军事以及工业领域中的各种应用,最高可实现1.2 GHz双核工作主频。P2020主要特点有:双核高性能Power Architecture e500核心,36位物理寻址,800 MHz至1.2 GHz时钟频率;三个10/100/1000 Mbps增強型三速以太网控制器,支持RGMII、SGMII接口;支持64位DDR2/DDR3 SDRAM存储器控制器。

2 P2020的Local Bus与外设互联

Local Bus总线一般采用数据/地址线复用的形式,使用时需要将总线的数据和地址分离出来再分别接到目标器件的数据和地址端口, 需要通过 Buffer 起来来进行驱动和隔离,通过用信号锁存器SN74ALVCH16373 来分离总线中的数据和地址。Local Bus总线上的数据读写采用异步传输模式对FPGA、显控GPU、串口扩展芯片进行数据读写。

需要注意的是P2020采用大端模式,外部设备采用小端模式,所以在使用大端模式总线连接外部器件时需要将地址线进行倒序,即最高位地址线与外部器件的最低地址位相连,最低地址位地址线与外部器件的最高地址位相连,其他依次连接。

3主控板电源设计

主控板实际功耗随环境温度变化有所不同,在常温下工作5W,在高温环境65℃下工作8W,本设计中可以提供宽输入直流电平5V~15V,板卡内需要提供3.3V、2.5V、1.35V、1.05V、1.2V。板卡选用的是ZL6105ALAF,LTM4644,LTC3617,其中特别推荐LTC3617,该器件能够为DDR3产生一个总线终端电压。可在VTT和VTTR上分别提供了?A (供应 / 吸收)的输出电流能力。

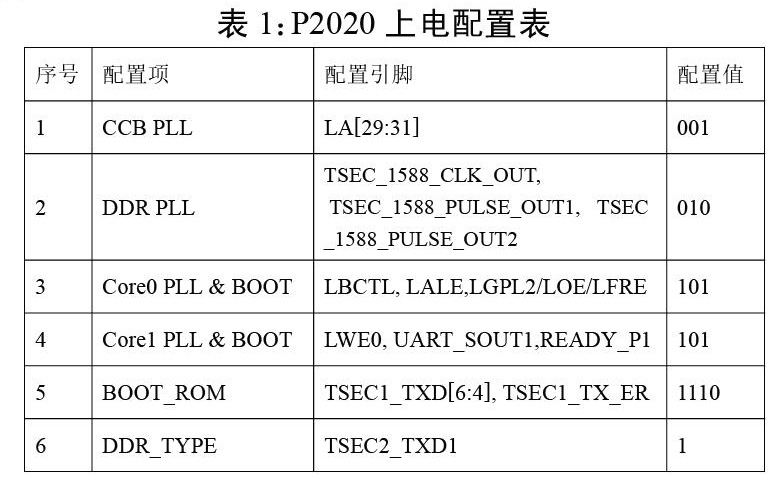

4 P2020的启动配置

P2020的内核时钟,DDR3工作时钟, CPU总线时钟等的设置是靠上下拉CPU的配置引脚来实现的。

P2020启动时需要注意是:硬启动是需要按一定时序来进行的,所以一般会借助FPGA来完成时序的控制。其中复位信号HRESET必须先高-后低-再高电平,不然无法正常启动。

5结论

本文详细介绍了基于P2020处理器的主控单元的硬件设计方案,该板卡已经应用在多个系统的综合通信平台上,在实际应用中表现出良好的稳定性,对PowerPC在嵌入式系统中开发应用具有较高的参考价值。

参考文献

[1] Freescale Semiconductor ,P2020 QorIQ Integrated Processor Reference Manual[M].2012

[2] 胡阳.基于POWERPC的嵌入式无线通信控制单元设计[D].北京:北京邮电大学,2015.

[3] 夏航,汪溢.基于多核处理器P2020的综合数据处理模块设计及应用[J].航空电子技术,2012.

- 美国对智利弗雷政府政策探析

- 近代连云市都市计划述论

- 铁路站厂的“差序化设置”与华北集镇的“差异化发展”

- 近代铁路交通视阈下商圈互动与郑州区域中心地的形成

- 历史合理性:全球化趋势下民族精神研究与培育问题再探讨

- 1960年代初江苏省农村家庭副业调整述论

- 抗战后国民党消弭学运策略论析

- “二七”大罢工时期的京汉铁路工人述论

- 汉宣帝与霍光的权力博弈探析

- 论苏联卫国战争时期女性在工业生产中的贡献

- 20世纪60年代美国黑人文艺运动研究

- 印度大起义与英国社会的反应

- 犹太社会与“大屠杀”的国际认知

- 探寻吾土吾民的生命足迹

- 浅析提高历史专业师范生教学技能的有效途径

- 全球史观下的民族院校世界现代史教学实践及思考

- 唐代长安的庙会与戏场

- 吕颐浩北伐的前前后后

- 民国时期中国东北关内移民与朝鲜移民活动比较研究(1911-1931)

- 近代英国圣公会在浙江的传教活动

- 九一八事变后孙科政府的对日绝交方案

- 论张作霖与日本关系的双重面相

- 中俄《北京条约》签订后清政府对三姓地区赫哲族的安边政策

- 晚清“巡警军”考析

- 《易》贵中正:刘沅《周易恒解》研究

- prealleging

- prealliance

- prealliances

- preallied

- preallies'

- preallies

- preallot

- prealloted

- prealloting

- preallots

- preallotted

- preallotting

- preallow

- preallowable

- preallowably

- preallowance

- preallowances

- preallowed

- preallowing

- preallows

- preallude

- prealluded

- prealludes

- prealluding

- preallusion

- 彼此了解而情谊深切

- 彼此了解,心意投合

- 彼此了解,心意投合,互相关心备至

- 彼此了解,心意相通

- 彼此互不关照,各奔前程

- 彼此互换

- 彼此互相照应

- 彼此交好

- 彼此交往的时间较久

- 彼此交情深厚

- 彼此产生隔阂

- 彼此亲密无间

- 彼此亲昵接近

- 彼此亲爱友好

- 彼此亲近,关系密切

- 彼此会面

- 彼此伸手相互握住

- 彼此依恋,不忍分别

- 彼此依附

- 彼此共处困境

- 彼此关爱

- 彼此关白

- 彼此关系密切

- 彼此关系密切,经常在一起

- 彼此关系很好,毫无矛盾